# AQUANTIA®

## AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C AQrate® Gen 4 Multi-Gigabit Ethernet PHY Transceiver

### **General Description**

The Aquantia® AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C AQrate PHYs are full-reach, low-power, high-performance, multi-gigabit, single-port Gen 4 Ethernet PHY transceivers that are designed with 14nm, multi-gate, FinFET process technology that supports the following network rates: 10GBASE-T/5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX/10BASE-Te.

Aquantia AQrate PHYs are compliant with both the IEEE<sup>®</sup> 802.3an/bz standard and the NBASE-T<sup>™</sup> Alliance PHY Specification to perform all of the physical layer functions required to implement 10GBASE-T/5GBASE-T/ 2.5GBASE-T/1000BASE-T/100BASE-TX/10BASE-Te transmission over 100+ meters of twisted pair cabling. The AQrate PHY family integrates such key features as Energy Efficient Ethernet (EEE), Precision Time Protocol (PTP)/1588v2, IEEE MAC Security (MACsec), Synchronous Ethernet (Sync-E), support for all PoE standards up to 100W, and support for jumbo packets up to 16KB in all operating modes.

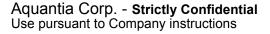

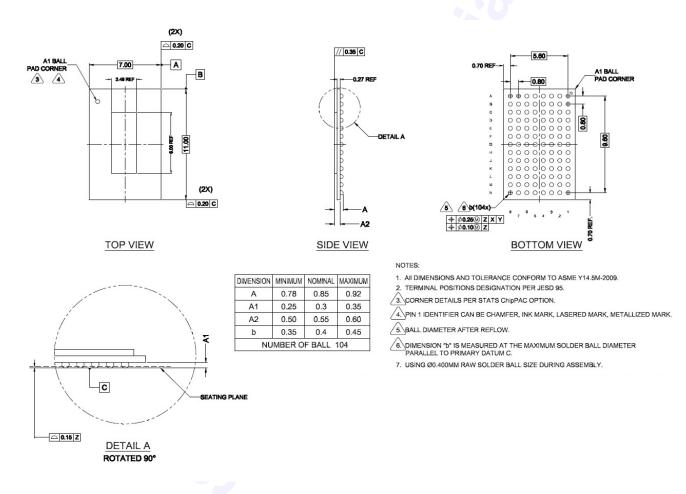

The AQR113-AQR114-AQR115 are pin-compatible, multi-gigabit, single-port PHYs housed in 7 mm x 11 mm, 104-pin, flip-chip BGA (FCBGA) packages, while the AQR113C-AQR114C-AQR115C PHY devices are pin-compatible, multi-gigabit, single-port PHYs housed in compact 7 mm x 7 mm, 64-pin FCBGA packages.

**Note:** For the remainder of this datasheet, the term *device* or *device family* can be used interchangeably to represent the AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C product line, unless a distinction needs to be made based on the specific package or supported features.

| Features                                                                                                                                                                                                                                                                                                                     | Benefits                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>AQR113/AQR113C:<br/>10GBASE-T/5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX/10BASE-Te</li> <li>AQR114/AQR114C:<br/>5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX/10BASE-Te</li> <li>AQR115/AQR115C:<br/>2.5GBASE-T/1000BASE-T/100BASE-TX/10BASE-Te</li> </ul>                                                               | <ul> <li>Pin-compatible low-power, high-performance, multi-gigabit,<br/>PHYs enable design flexibility and reuse</li> </ul>                                                                                                                                                                                        |

| <ul> <li>IEEE 802.3an/bz and NBASE-T featuring AQrate technology</li> <li>10GBASE-T: 100 meters over Augmented Cat 6 (Cat 6A) and Cat 7, 55 meters over Cat 6, and best effort over Cat 5e</li> <li>5GBASE-T, 2.5GBASE-T: over 100 meters of Cat 5e or better cabling</li> </ul>                                             | <ul> <li>Ability to support highest data rate possible with a given cable<br/>environment while reducing power and latency</li> <li>5G and 2.5G operation over legacy infrastructure, while<br/>delivering backward compatibility with existing equipment</li> </ul>                                               |

| <ul> <li>Energy-Efficient Ethernet (EEE)</li> <li>MACsec (IEEE 802.1ae, MAC security standard)         <ul> <li>Full support for Advanced Encryption Standard (AES-256) and stand-alone operation</li> <li>PTP/1588v2</li> <li>Synchronous Ethernet (Sync-E), ITU-T standard in cooperation with IEEE</li> </ul> </li> </ul> | <ul> <li>EEE lowers overall power consumption and lowers equipment<br/>operating costs</li> <li>MACsec provides for secure, encrypted data communications<br/>across networks</li> <li>PTP/1588v2 provides for timing accuracy across the network</li> <li>Sync-E synchronizes clock signals on the PCB</li> </ul> |

| <ul> <li>Integrated Wake-on-LAN (WoL) Support</li> <li>Compliant to Microsoft Network Device Class specification</li> <li>Energy Detect</li> <li>Places PHY in a low-power state when there is no active link partner</li> </ul>                                                                                             | <ul> <li>Integrated packet filtering enables sub-1W support in<br/>100BASE-TX mode</li> <li>Provides additional power savings when no active link partner is<br/>present</li> </ul>                                                                                                                                |

| Built-in Thermal Management     On-chip thermal sensor with alarm and warning thresholds                                                                                                                                                                                                                                     | Enables deployment in thermally constrained environments                                                                                                                                                                                                                                                           |

### AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C AQrate® Gen 4 Multi-Gigabit Ethernet PHY Transceiver

| Features                                                                                                                                                                                                                                                                                            | Benefits                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>7 mm x 11 mm (AQR113-AQR114-AQR115)</li> <li>104-pin FCBGA package</li> <li>0.8 mm ball pitch</li> <li>Low thermal resistance</li> <li>7 mm x 7 mm flip-chip (AQR113C-AQR114C-AQR115C)</li> <li>64-pin FCBGA package</li> <li>0.8 mm ball pitch</li> <li>Low thermal resistance</li> </ul> | <ul> <li>Low cost</li> <li>Flexible heat-sinking</li> <li>Compatible with volume PCB manufacturing</li> </ul>                                                                                                                                                                          |

| IEEE      802.3-2012 compliant auto-negotiation                                                                                                                                                                                                                                                     | Interoperable with existing Ethernet infrastructure                                                                                                                                                                                                                                    |

| <ul> <li>External SPI FLASH interface with optional FLASH-less operation</li> <li>At-manufacture FLASH burn capability</li> </ul>                                                                                                                                                                   | <ul> <li>Reduces BOM cost as one or no FLASH devices required</li> <li>Enables firmware download/upgrade and FLASH image loading during manufacturing</li> </ul>                                                                                                                       |

| <ul> <li>50MHz Crystal or LVDS oscillator clock operation         <ul> <li>Integrated ultra-low phase noise synthesizer</li> <li>50MHz output clock signal</li> <li>156.25MHz LVDS oscillator clock operation</li> </ul> </li> </ul>                                                                | <ul> <li>Crystal operation allows for lower BOM cost</li> <li>Outputs primary and secondary 50MHz and 156.25MHz received reference output for Sync-E</li> </ul>                                                                                                                        |

| Advanced Cable Diagnostics     On-chip high-resolution cable analyzer                                                                                                                                                                                                                               | Enables the deployment of meaningful cable analysis tools for<br>debugging installation problems                                                                                                                                                                                       |

| <ul> <li>High-Performance full KR (with autonegotiation)/XFI/USXGMII/5000BASE-R/<br/>2500BASE-X/SGMII I/F with AC-JTAG/1000BASE-X</li> <li>Capable of rate adapting all rates into KR/XFI via PAUSE and 100M/1G into<br/>2500BASE-X</li> </ul>                                                      | <ul> <li>Ensures trouble-free operation over a range of interconnect<br/>scenarios (includes parallel detect and downshift capabilities)</li> <li>Comprehensive interface support         <ul> <li>Supports legacy and next generation MACs/switches/processors</li> </ul> </li> </ul> |

| <ul> <li>Advance Loopback and Diagnostic Capability</li> <li>Flexible on-chip BERT</li> <li>Full 1 second packet counters and CRC-32 checkers</li> </ul>                                                                                                                                            | Enables extensive system test and debug with remote loopback control                                                                                                                                                                                                                   |

| Integrated MDI Filter and Advanced RFI Cancellation     Eliminates external filter components                                                                                                                                                                                                       | Robust Radio Frequency Interference (RFI) performance     Resilient operation when exposed to RFI                                                                                                                                                                                      |

## **Detailed Description**

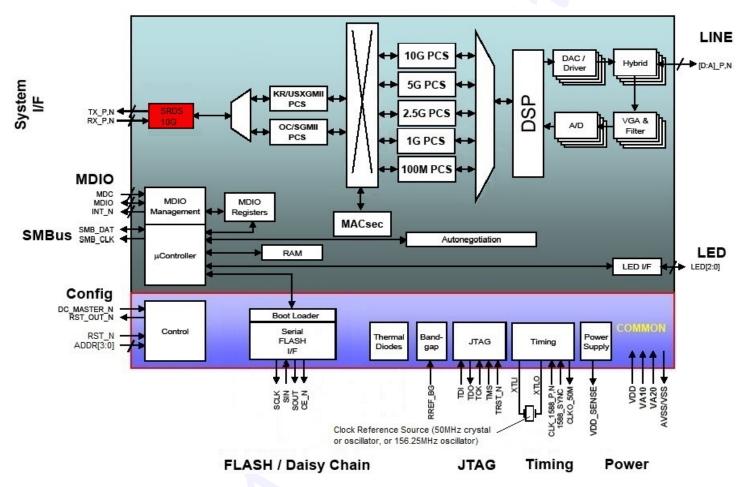

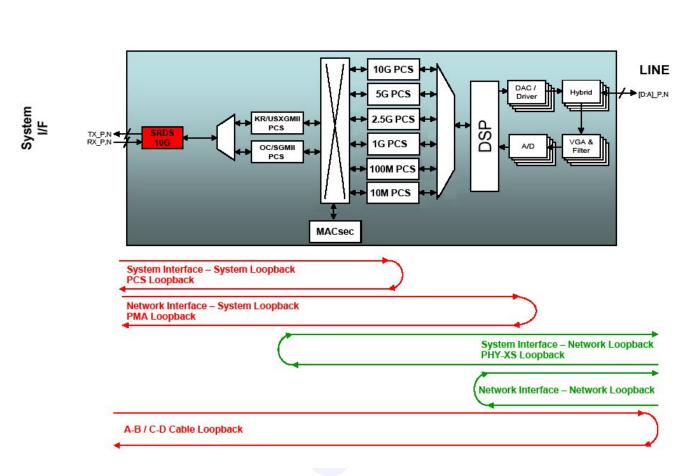

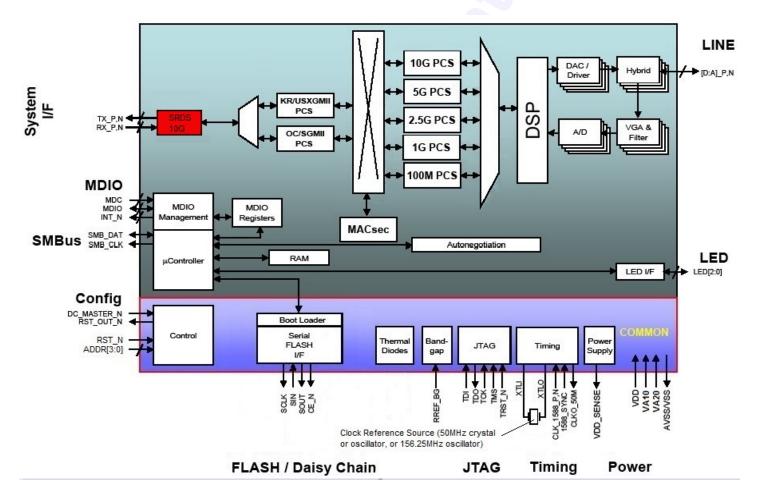

A block diagram of the device family is shown in Figure 1 on page 3. Its port utilizes a common analog front-end for all supported network rates, and a common system interface (configurable as KR or XFI in 10G, 2500BASE-X in 2.5G, and SGMII in 1G or 100M, or all rates via USXGMII/KR). In the transmit direction in 10G, and AQrate modes, data from the system interface is equalized and received. This data is then mapped into a virtual internal XGMII interface where blocks of two XGMII frames (32 bits of data + 4 bits of control) are encoded into a single 65B block, using the 64B/65B encoding scheme specified in Clause 55. In 10G mode, fifty of these 65B blocks are aggregated together, along with a prepended auxiliary bit, and an appended CRC-8 to form the 3259-bit 10GBASE-T transmission frame payload.

This payload is then encoded using a combination of Low-Density Parity-Checking (LDPC) encoding and coset partitioning, with the LDPC encoding adding an additional 325 systematic check bits to produce a 3584-bit 10GBASE-T transmission frame. The coset partitioning effectively divides the frame up into 512 7-bit symbols, where the upper 3 bits are uncoded and describe the coset, while the lower 4 bits are coded and identify an element within the coset. These 8 cosets are then mapped onto a 128-DSQ constellation (a 16 x 16 checkerboard pattern) which is physically encoded as two back-to-back PAM-16 symbols.

These symbols are then coded using the Tomlinson Harashima Precoded (THP) technique, filtered, and sent out over the four twisted pairs in the cable. AQrate 5G transmission is done in a similar fashion, but it uses a fully LDPC encoded 320ns PAM-16 frame containing twenty-five 65B blocks.

The AQrate 2.5G transmission is also similar, but it uses a 640ns frame that contains twenty-five 65B blocks. In the receive direction in 10G, 5G, and 2.5G modes, PAM-16 coded symbols enter the device family from the line interface and pass through the hybrid, which provides transmit/receive isolation. These symbols are then filtered and amplified prior to being sampled by four, high-speed, high-precision Analog-to-Digital (A/D) converters.

The outputs of these A/D converters are then passed through an extensive set of adaptive equalizers which provide both cross-talk and echo cancellation. After timing is recovered, the data from the four channels is aligned and merged together to form the original, but noisy transmission frames.

In all three modes, the data is decoded using an LDPC decoder. However, in 10G mode the data is further sliced using knowledge of the coset partitioning and 128-DSQ mapping to produce the original 10GBASE-T transmission frame payload. The CRC-8 over this payload is then checked to ensure integrity of the uncoded bits.

Finally, in all schemes, the auxiliary bit is stripped, 65B blocks remapped into XGMII blocks, and the received Ethernet data transmitted out the MAC interface. When operating in 1G or 100M modes, receive data from the analog front-end is routed to either the 1G or 100M PCS where timing is recovered and equalization performed. In 1G mode, Viterbi decoding is also done.

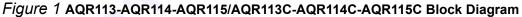

From here, the data passes across a virtual GMII interface to the system interface which is either SGMII, or USXGMII mode on logical Lane 0. In the transmit direction, if 1G/100M data is received on either the SGMII, or USXGMII interface, it is passed through the 1G or 100M PCS, and is then transmitted by the common analog front-end. Figure 2 shows a typical system-level block diagram of a 10GBASE-T channel built using this device.

#### *Figure 2* AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C System Block Interconnect

On the line side of the device family, a robust interface providing good common-mode rejection and electrical protection against cable discharge is implemented. On the MAC side, the device family provides a robust SerDes interface that supports 10G with configurable pre-emphasis and receive equalization.

For test coverage, this interface also incorporates AC JTAG. Control over the chip is done via an external C-language application program interface (API) that provides an easy-to-use abstraction of the device family, and via an MDIO interface provides the standard Clause 45 register set for control of 10GBASE-T devices.

On-chip, the device family contains a 32-bit microcontroller which manages the state machines and operation of the various elements within the chip. Consequently, there is a great deal of flexibility afforded to the end user because of the presence of this microcontroller, and as such the device family offers a high degree of control and flexibility. The image for the microcontroller is stored either in an optional external SPI FLASH, or loaded at boot time via the MDIO interface (MDIO boot-load).

This interface also provides the user the capability of directly programming the FLASH during manufacturing. In addition to the Ethernet interfaces, the device family provides three 20mA LED outputs for the port that are software configurable to respond to a variety of conditions such as link activity and connection status. Clocking for the device family is provided from a 50MHz external crystal or LVDS differential oscillator or a 156.25MHz LVDS oscillator.

To better assist the system designer in deploying the device family, Aquantia provides a reference design (with part numbers, schematics, and layout) that is optimized for performance, efficiency, and cost. The power for the device family is provided from its analog and digital supply voltages, and it supports an I/O voltage level of either 1.8V or 3.3V.

### Package Feature Comparison

This section lists the package feature comparison between the 7 mm x 11mm and the 7 mm x 7 mm packages for the two devices, respectively.

| Feature                                            | AQR113-AQR114-AQR115                                                                     | AQR113C-AQR114C-AQR115C                                                                     |

|----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Device Package Size                                | 7 mm x 11 mm                                                                             | 7 mm x 7 mm                                                                                 |

| Device Package Type                                | 104-pin FCBGA (8 rows x 13 rows)                                                         | 64-pin FCBGA (8 rows x 8 rows)                                                              |

| Number of Serial Management<br>Interface Addresses | ADDR[3:0]<br>Up to 16 unique PHY addresses                                               | ADDR[3]<br>Up to 2 unique PHY addresses                                                     |

| PTP/1588v2 Support                                 | Yes                                                                                      | No                                                                                          |

| Network Rates Supported                            | <ul> <li>AQR113 (6-speed)</li> <li>AQR114 (5-speed)</li> <li>AQR115 (4-speed)</li> </ul> | <ul> <li>AQR113C (6-speed)</li> <li>AQR114C (5-speed)</li> <li>AQR115C (4-speed)</li> </ul> |

#### Table 1: Package Feature Comparison

#### **Package Information**

The single-port AQR113-AQR114-AQR115 PHY devices are packaged in a 0.8 mm pitch, 7 mm x 11 mm over-molded, 104-pin FCBGA (8 rows x 13 rows).

The single-port AQR113C-AQR114C-AQR115C PHY devices are packaged in a 0.8 mm pitch, 7 mm x 7 mm over-molded, 64-pin FCBGA (8 rows x 8 rows).

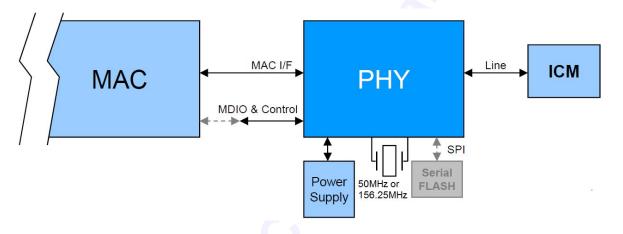

Both the 7 mm x 11 mm and 7 mm x 7 mm packages are marked as shown in Figure 3, and these packages are described in Table on page 6

#### Figure 3 Part Marking

| Part of Code | Description                                                                    | Available Options                                                                         |

|--------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| AQRxxxx      | Product Name Please refer to the master part number specification for specific |                                                                                           |

| XX           | Product Revision Level                                                         | Identifies the base and metal layer revision levels                                       |

| YY           | Temperature Grade                                                              | C = Commercial                                                                            |

| X            | Optional Customer-<br>Specific Indicator                                       | Field reserved as an "add mark" field for customer-specific versions of Aquantia products |

#### **Table 2: Part Marking Description**

### **Release Notes**

Refer to the *Aquantia AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C Release Notes* to determine the latest product revision level device being supported, a full list of known issues, and any errata for both package versions of the AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C family of devices.

### **Ordering Information**

| Device              | Description                                    | Ordering Part Number |  |  |

|---------------------|------------------------------------------------|----------------------|--|--|

| 7 mm x 11 mm Pa     | 7 mm x 11 mm Package                           |                      |  |  |

| AQR113              | 6-Speed Commercial Temperature Grade, RoHS 6/6 | AQR113-XX-C          |  |  |

| AQR114              | 5-Speed Commercial Temperature Grade, RoHS 6/6 | AQR114-XX-C          |  |  |

| AQR115              | 4-Speed Commercial Temperature Grade, RoHS 6/6 | AQR115-XX-C          |  |  |

| 7 mm x 7 mm Package |                                                |                      |  |  |

| AQR113C             | 6-Speed Commercial Temperature Grade, RoHS 6/6 | AQR113C-XX-C         |  |  |

| AQR114C             | 5-Speed Commercial Temperature Grade, RoHS 6/6 | AQR114C-XX-C         |  |  |

| AQR115C             | 4-Speed Commercial Temperature Grade, RoHS 6/6 | AQR115C-XX-C         |  |  |

**Note:** The "XX" designation in the ordering part number signifies the revision of the device. Please contact your local Aquantia sales representative or FAE for information on the latest device revision.

### **Contact Information**

For more product-related information, use of the following methods to contact your Aquantia Account Manager or Support:

INTERNET: Home: http://www.aquantia.com

E-MAIL: sales@aquantia.com, info@aquantia.com

ADDRESS: Aquantia Corp., 91 East Tasman Drive, Suite 100, San Jose, CA 95134

PHONE/FAX: 408-228-8300, FAX 408-597-8499

#### AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C AQrate® Gen 4 Multi-Gigabit Ethernet PHY Transceiver

#### **Revision History**

| Revision | Date           | Chapter/Section           | Description                                                                          |

|----------|----------------|---------------------------|--------------------------------------------------------------------------------------|

| 1.0      | March 2018     |                           | Initial release                                                                      |

| 1.0.1    | June 2018      | Introduction<br>Chapter 2 | Revised company address<br>Revised Table 2.5, Serial FLASH Signals                   |

| 1.0.2    | June 2018      | Chapter 2                 | Revised Table 2.18 and Table 2.19<br>Revised package drawing for 7 mm x 11 mm device |

| 1.0.3    | June 2018      | Chapter 2                 | Revised pin-signal tables                                                            |

| 1.0.4    | July 2018      | Introduction              | Revised supported speeds                                                             |

| 1.0.5    | August 2018    | Chapter 5                 | Revised thermal specifications                                                       |

| 1.0.6    | September 2018 | Chapter 5                 | Added standard reflow profile for lead-free packages material                        |

| 1.0.7    | October 2018   | Introduction              | Revised part marking figure per corporate policy to remove trademarks                |

## **Trademarks and Copyrights**

PROPRIETARY AND CONFIDENTIAL: This document is provided by Aquantia Corp. in connection with its products. Disclosure, reproduction, distribution, and use of the contents of this document is permitted only by the intended recipient(s) and only as expressly authorized by Aquantia. No license under any patents or other intellectual property rights of Aquantia is granted by this document. Aquantia may change the information in this document and any of its products and services at any time without notice.

DISCLAIMER OF WARRANTIES: Performance specifications and other information provided by Aquantia are provided "AS IS" without warranties of any kind. Aquantia disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty of accuracy or completeness, or any warranty arising from course of performance, course of dealing or usage in trade.

BUYER RESPONSIBILITIES: Unless specifically stated, Aquantia products are not authorized or warranted to be suitable for use in medical, military, automotive, aeronautical or life support equipment, nor in applications where the failure or malfunction of our product can be reasonably expected to result in personal injury, death or property damage. Aquantia accepts no liability for inclusion and/or use of our products in such equipment or applications and any such inclusion is at your own risk.

Aquantia is a registered trademark of Aquantia Corp., and Aquantia and the Aquantia logo are trademarks of Aquantia Corp. Other trademarks in this document are the property of their respective owners.

Copyright © 2018 Aquantia Corp. All Rights Reserved.

#### **Strictly Confidential**

AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C Revision 1.0.7 - October 2018

| Section                                                                                                                                                                                                                                  | Page                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1 Overview                                                                                                                                                                                                                               |                                                      |

| Introduction                                                                                                                                                                                                                             |                                                      |

| General Deployment                                                                                                                                                                                                                       |                                                      |

| Mechanical<br>Power Supplies<br>Reset<br>Clocks<br>FLASH<br>Power-On Default Values<br>SerDes and MDI Configuration                                                                                                                      |                                                      |

| SerDes                                                                                                                                                                                                                                   | 19                                                   |

| Power-On                                                                                                                                                                                                                                 |                                                      |

| Cable and Board Diagnostics                                                                                                                                                                                                              | 21                                                   |

| Debug and Diagnostics Tools                                                                                                                                                                                                              | 21                                                   |

| API and Programming Tools                                                                                                                                                                                                                |                                                      |

| MACsec                                                                                                                                                                                                                                   |                                                      |

| General Features                                                                                                                                                                                                                         |                                                      |

| Energy Efficient Ethernet                                                                                                                                                                                                                |                                                      |

| Precision Time Protocol (PTP)                                                                                                                                                                                                            |                                                      |

| 2 Hardware Interfaces                                                                                                                                                                                                                    | 37                                                   |

| Package Pin-Signal Differences                                                                                                                                                                                                           |                                                      |

| Management Interface                                                                                                                                                                                                                     |                                                      |

| IDLE (Idle Condition)<br>PRE (Preamble)<br>Normal Operation<br>Preamble Suppression<br>ST (Start Of Frame)<br>OP (Operation Code)<br>PHYAD (PHY Address)<br>MMDAD (MMD Address)<br>TA (Turnaround)<br>ADDRESS/DATA<br>Interrupt<br>Reset | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Reset                                                                                                                                                                                                                                    |                                                      |

| Section                                                                                                                          | Page                                   |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Serial Flash                                                                                                                     | 44                                     |

| SPI FLASH Interface                                                                                                              |                                        |

| Firmware                                                                                                                         | 48                                     |

| Provisionable Default                                                                                                            | 49                                     |

| Daisy Chain                                                                                                                      | 50                                     |

| SerDes                                                                                                                           | 51                                     |

| SerDes System Interface (I/F) Start-Up                                                                                           | 52                                     |

| 10G Mode<br>2500BASE-X Mode<br>1000BASE-X Mode<br>XSGMII Mode<br>USXGMII Mode<br>All-Off Mode<br>Interrupts<br>XSGMII<br>USXGMII | 53<br>53<br>54<br>55<br>55<br>56<br>56 |

| MDI                                                                                                                              | 59                                     |

| Timing                                                                                                                           | 60                                     |

| LED                                                                                                                              | 63                                     |

| Reference Resistors                                                                                                              | 63                                     |

| JTAG/Test                                                                                                                        | 64                                     |

| Debug                                                                                                                            | 65                                     |

| Power                                                                                                                            | 65                                     |

| Reserved                                                                                                                         | 68                                     |

| Pin-Out                                                                                                                          | 68                                     |

| 3 Timing                                                                                                                         | 71                                     |

| MDIO                                                                                                                             | 71                                     |

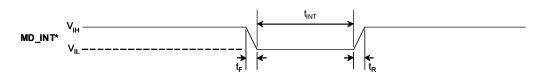

| Interrupt                                                                                                                        | 72                                     |

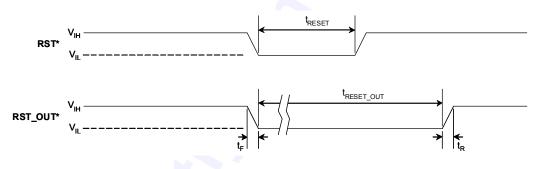

| Reset                                                                                                                            | 72                                     |

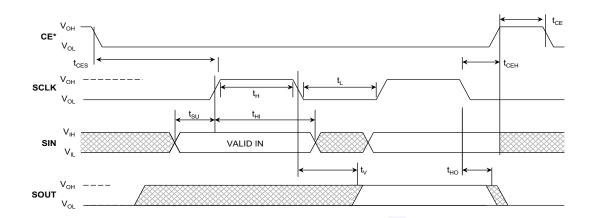

| SPI                                                                                                                              | 73                                     |

| SerDes                                                                                                                           | 74                                     |

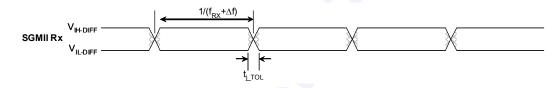

| SGMII Transmit                                                                                                                   | 75                                     |

\_

| Section Pa                                                                       | age      |

|----------------------------------------------------------------------------------|----------|

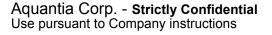

| SGMII Receive                                                                    | 75       |

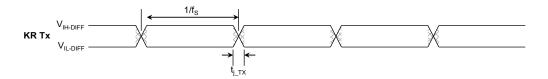

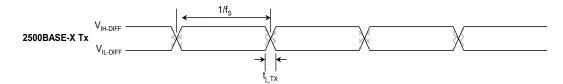

| KR Transmit                                                                      | 76       |

| KR Receive                                                                       | 76       |

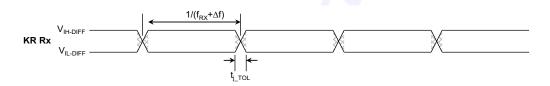

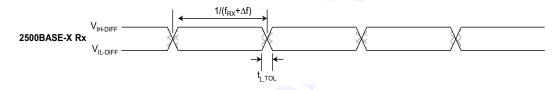

| 2500BASE-X Transmit                                                              | 77       |

| 2500BASE-X Receive                                                               | 77       |

| Clocks                                                                           | 78       |

| Input                                                                            | 79       |

| JTAG/Test                                                                        |          |

| 4 Electrical Specifications                                                      | 51       |

| Absolute Maximum Ratings 8                                                       | 31       |

| Recommended Operating Conditions                                                 | 31       |

| Power                                                                            | 32       |

| Operating Modes                                                                  |          |

| Power Supplies                                                                   | 34       |

| VA20, VA10, and VDD Supply Specifications                                        | 84       |

| Other Power Supplies 8                                                           |          |

| VDD_IO Supply Specifications                                                     | 85       |

| Steady-State Operating Conditions 8                                              | 35       |

| Typical Steady-State Operating Conditions                                        | 85<br>86 |

| Instantaneous Current Consumption 8                                              | 36       |

| Support for Low-Power Modes 8                                                    | 37       |

| Management Interface                                                             | 37       |

| I/O8                                                                             | 39       |

| Serial FLASH                                                                     | 90       |

| SerDes                                                                           | 90       |

| Line (MDI)                                                                       | 91       |

|                                                                                  | 92       |

| Input Clock Pins XTAL_I and XTAL_O<br>Input Clock Pins CLK_1588_P and CLK_1588_N | 92<br>92 |

| Section                                        | Page |

|------------------------------------------------|------|

| Reference Resistors                            | 93   |

| 5 Package                                      | 95   |

| Mechanical                                     | 95   |

| Thermal                                        | 97   |

| Theta Js                                       |      |

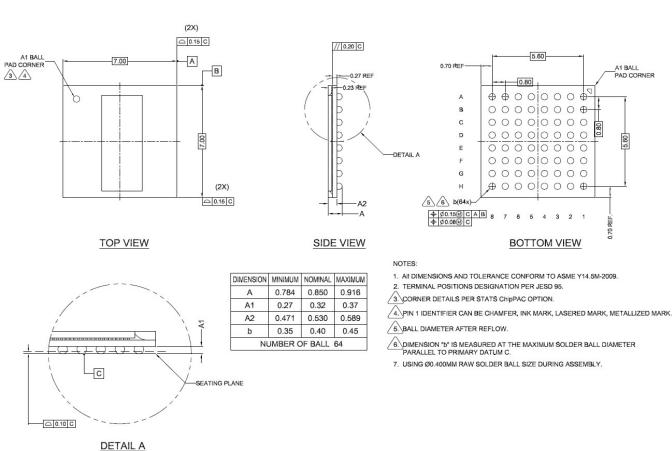

| Standard Reflow Profile for Lead-Free Packages | 97   |

| 6 Register Map                                 | 101  |

| Introduction                                   | 101  |

| Register Structure                             | 102  |

| Format and Nomenclature                        | 103  |

| Structure                                      | 104  |

| Register Tables Documentation                  | 106  |

| References                                     | 107  |

## List of Figures

| Figure                                                                    | Page |

|---------------------------------------------------------------------------|------|

| AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C<br>Block Diagram             | 3    |

| AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C System<br>Block Interconnect |      |

| Part Marking                                                              | 5    |

| Loopbacks                                                                 |      |

| User Priority Resolution                                                  |      |

| EtherType and VLAN Parsing Algorithm                                      | 28   |

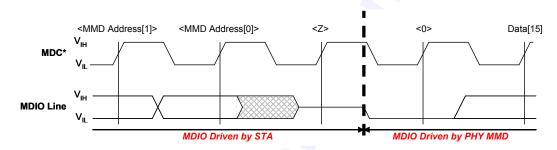

| MDIO Bus Turn-Around During Read Operations                               | 42   |

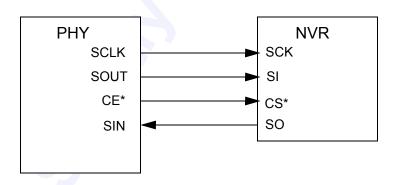

| SPI Interface Block Diagram                                               | 46   |

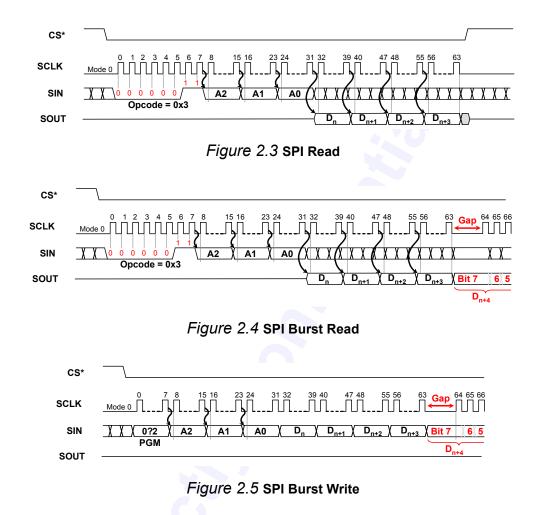

| SPI Read                                                                  | 47   |

| SPI Burst Read.                                                           | 47   |

| SPI Burst Write                                                           | 47   |

| AQR113-AQR114-AQR115 Pin-Out Drawing                                      | 69   |

| AQR113C-AQR114C-AQR115C Pin-Out Drawing                                   | 70   |

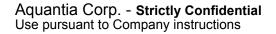

| MDIO Setup and Hold Times                                                 | 71   |

| Interrupt Timing Diagram                                                  | 72   |

| Reset Timing Diagram                                                      | 72   |

| SPI Timing Diagram                                                        | 73   |

| SGMII Transmit Timing Diagram                                             | 75   |

| SGMII Receive Timing Diagram                                              | 75   |

| KR Transmit Timing Diagram                                                | 76   |

| KR Receive Timing Diagram                                                 | 76   |

| 2500BASE-X Transmit Timing Diagram                                        | 77   |

| 2500BASE-X Receive Timing Diagram                                         | 77   |

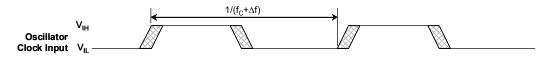

| 50MHz Input Timing Diagram                                                | 78   |

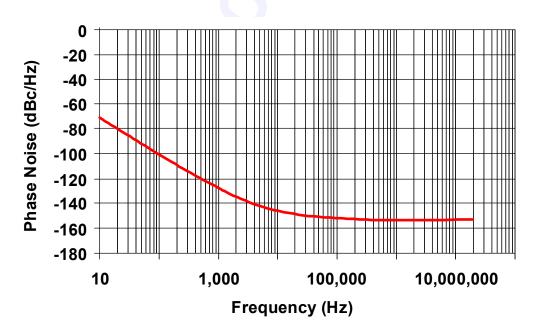

| 50.000MHz Phase Noise Mask                                                | 78   |

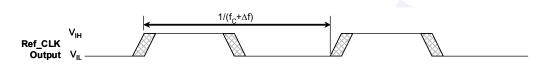

| 50MHz Reference Clock Output Timing Diagram                               | 79   |

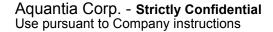

| JTAG/Test Timing Diagram                                                  | 80   |

## List of Figures

| Page                                        | Figure |

|---------------------------------------------|--------|

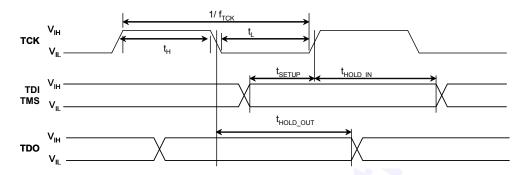

| Power Versus Time                           | 83     |

| AQR113-AQR114-AQR115 Mechanical Drawing     |        |

| AQR113C-AQR114C-AQR1115C Mechanical Drawing |        |

| Reflow Profile                              |        |

| MDIO Manageable Devices Block Diagram       | 101    |

\_\_\_\_\_

## List of Tables

| Table                                              | Page |

|----------------------------------------------------|------|

| System I/F Idle Options                            | 20   |

| System Interface SerDes Operating Modes            | 20   |

| Additional Ingress MACsec Statistics               | 24   |

| Additional Egress MACsec Statistics                | 25   |

| "Per SCI" 32-Bit Mapping                           | 26   |

| MAC Statistics                                     | 32   |

| Key Pin-Signal Package Differences.                | 37   |

| Management Interface Signals                       | 38   |

| MDIO Frame Format                                  | 40   |

| Power-On Reset Thresholds for Core Supply Voltages | 43   |

| Serial FLASH Signals                               | 45   |

| Daisy Chain Signals                                | 50   |

| SerDes Signals                                     | 51   |

| KR Diagnostic Pattern Capabilities                 | 52   |

| SGMII Diagnostic Pattern Capabilities              | 52   |

| XSGMII Base Page                                   | 57   |

| USXGMII Base Page                                  | 58   |

| MDI Signals                                        | 59   |

| Timing Signals                                     | 61   |

| LED Signals.                                       |      |

| Reference Resistor Signals.                        | 63   |

| JTAG/Test Signals                                  |      |

| Debug Signals (7 mm x 11 mm Package)               |      |

| Power Signals                                      |      |

| Reserved Signals (7 mm x 11 mm Package)            |      |

| MDIO Timing                                        |      |

| Interrupt timing                                   |      |

| Reset Timing                                       |      |

| SPI Timing                                         |      |

| SerDes Receive Jitter Tolerance Specifications     |      |

| SerDes Transmit Jitter Tolerance Specifications    |      |

| SGMII Transmit Timing                              |      |

| SGMII Receive Timing.                              |      |

| KR Transmit Timing                                 |      |

| KR Receive Timing                                  |      |

| 2500BASE-X Transmit Timing                         |      |

| 2500BASE-X Receive Timing                          |      |

| 50.000MHz Input Timing                             | 78   |

## List of Tables

| Table                                                           | Page |

|-----------------------------------------------------------------|------|

| 50MHz Reference Clock Output Timing                             | 79   |

| JTAG/Test Timing                                                | 80   |

| Device Family Absolute Maximum Ratings                          | 81   |

| Device Family Recommended Operating Conditions                  | 81   |

| Example Latency Values per Network Rates                        | 84   |

| VA20, VA10, and VDD Electrical Parameters.                      | 84   |

| VDD_IO Electrical Parameters                                    | 85   |

| Typical Steady-State Parameters                                 |      |

| Maximum Steady-State Parameters                                 | 86   |

| Training Parameters                                             |      |

| Low-Power Mode Support                                          | 87   |

| 1.8V Mode MDIO Electrical Interface Characteristics             | 88   |

| 70% / 30% VDD_IO Mode MDIO Electrical Interface Characteristics |      |

| I/O Pin Electrical Parameters                                   |      |

| SPI Pin Capacitance                                             |      |

| SPI DC Characteristics.                                         |      |

| SerDes Transmitter Characteristics                              |      |

| MDI Electrical Parameters                                       | 91   |

| SerDes Receiver Characteristics                                 |      |

| LVDS 50MHz Input Electrical Parameters                          |      |

| CLK_1588 Input Electrical Parameters                            |      |

| Bandgap Reference Resistor Electrical Parameters                |      |

| Theta Js                                                        |      |

| Pb-Free Reflow Profile Guidelines                               |      |

| MMD Device Addresses                                            |      |

| MDIO Register Space Bit Field Types                             |      |

| Register Layout                                                 |      |

| Terms Used within the Register Layout                           | 105  |

## Overview

## 1.1 Introduction

The AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C is a single-port, low-power, high-performance, full-reach, multi-gigabit Gen 4 PHY device family fabricated using 14nm, multi-gate, FinFET process technology. This chapter provides an overview of the device family and its operating modes.

This device family is designed to perform as a cost-competitive, stand-alone, 10G-100Mbps solution for a wide variety of NIC, switch, and LAN-on-Motherboard (LoM) applications that require multi-gigabit capability. The AQR113 and AQR113C devices support the following network rates:

- 10GBASE-T

- 5GBASE-T

- 2.5GBASE-T

- 1000BASE-T

- 100BASE-TX

- 10BASE-Te

The AQR114-AQR114C are 5-speed devices that support 5GBASE-T and all lower listed network rates. The AQR115-AQR115C are 4-speed devices that support 2.5GBASE-T and all lower listed network rates.

**Note:** For the remainder of this datasheet, the term *device* or *device family* can be used interchangeably to represent the following device family: AQR113, AQR114, AQR115, AQR113C, AQR114C, and AQR115C, unless a distinction needs to be made based on a specific package or supported features.

## **1.2 General Deployment**

This section briefly touches on the hardware implementation. For more detailed hardware design information, please see the *Aquantia Hardware Design Guide* (see "Hardware Design Guide", Aquantia Corporation" on page 107).

## 1.2.1 Mechanical

The AQR113-AQR114-AQR115 devices are packaged in a 7 mm x 11 mm, flip-chip 104-pin BGA (8 rows x 13 rows), and the AQR113C-AQR114C-AQR115C devices are packaged in a 7 mm x 7 mm, flip-chip 64-pin BGA (8 rows x 8 rows).

The die is rated to operate up to 108°C junction temperature, so engineering an appropriate thermal solution for the target system is designed so that it is a straight-forward task. For specific thermal values, see Thermal" on page 97.

## 1.2.2 Power Supplies

The device family utilizes four power supplies:

- A 0.7V digital supply (VDD)

- Two analog supplies: 1.0V and 2.0V (VA10 and VA20, respectively)

- An I/O supply (VDD\_IO) with two voltage options (1.8V or 3.3V)

All supplies should come up within 100ms from the first rail rising to the last rail reaching its 70% voltage level. The proper power-up sequence requires the VDD and 1.0V rails reach nominal voltage levels in any order first, followed by the other power rails in any order (this same order *must* be followed for the power-down sequence).

For the I/O supply, the device family offers a configurable VDD\_IO that supports either 1.8V or 3.3V, and this will set the logic thresholds for the I/O at 70%/30% of its voltage.

Note: AVSS, VSS, and VSS\_SRDS *must* be tied to the same ground plane.

## 1.2.3 Reset

The device family supports on-chip power-on reset generation, and it is also capable of supplying this reset to the rest of the system via a RST\_OUT\_N pin.

## 1.2.4 Clocks

The device family supports using several clocking options: a 50MHz crystal, a 50MHz LVDS oscillator, or a 156.25MHz LVDS oscillator to synthesize all of the required clocks. Supported clocking includes:

- PHY can perform operations using a single, 50MHz external crystal with an absolute accuracy of ±50pmm; only one crystal clock is required per common block.

- PHY can perform differential operations using a single, 50MHz LVDS oscillator with an absolute accuracy of ±50pmm, and the PHY provides 100Ω internal termination for this clock input (only one 50MHz LVDS oscillator is needed for the single version of the PHY).

PHY can perform differential operations using a single, 156MHz LVDS oscillator with an absolute accuracy of ±50pmm, and the PHY provides 100Ω internal termination for this clock input (only one oscillator is needed for the single-port version of the PHY).

**Note:** The supported output for synchronous Ethernet (Sync-E) operations in the device family is either 156.25MHz or 50MHz depending on the input clock source.

## 1.2.5 FLASH

The device family is capable of operating with a 512KByte (4Mbit) or larger SPI serial FLASH for autonomous operation, or of being boot-loaded via the MDIO interface. In both cases, the image stored in FLASH and the MDIO boot-load image are identical. If autonomous operation is not a requirement, and the target system is capable of providing the boot-load image, the FLASH can be eliminated.

The FLASH I/O operating voltage level *must* be the same as the PHY's VDD\_IO voltage level. If boot-loading is desired, it is possible to gang-load multiple parts via a broadcast MDIO address in the device family.

## 1.2.6 Power-On Default Values

The device family supports 10GBASE-T mode and other modes covered by IEEE 802.3an/bz, and includes a fixed set of hardware default values that exist in the chip for all its configurable registers. In addition, its firmware is capable of storing in its boot image (or in a separate image to keep the base firmware constant across multiple platforms) any change to these defaults effectively allows the user to configure the chip to come out of reset in the desired operating state.

## 1.2.7 SerDes and MDI Configuration

To offer routing flexibility on the SerDes interface, the device family is capable of performing polarity inversions<sup>†</sup>. On the line side, in addition to fully supporting MDI/MDI-X and automatic polarity correction, this device family also supports lane swapping of the ABCD pairs that enables easy board routing with different magnetics pin-outs.

## 1.3 SerDes

The device family is designed for use in conjunction with a multi-speed MAC chip. Table 1.1, details the supported system interface (I/F) idle options, and Table 1.2 on page 20, lists the SerDes operating modes supported by the device family's system interface (I/F).

<sup>†</sup> Note that polarity inversion is also referred to as "Lane Invert" in the register map.

| System I/F Idle Mode | Notes                                               |

|----------------------|-----------------------------------------------------|

| Off                  | SerDes turns on at selected operating mode for rate |

| XFI + USXGMII        |                                                     |

| KR + USXGMII         |                                                     |

#### Table 1.1 System I/F Idle Options

This PHY device family includes a single SerDes lane per port that supports 10G, and it supports the following SerDes modes listed in Table 1.2.

|         | System Interface SerDes Operating Modes |                                                    |          |   |          |            |

|---------|-----------------------------------------|----------------------------------------------------|----------|---|----------|------------|

| Rates   | USXGMII                                 | USXGMII XFI 5000BASE-R 2500BASE-X SGMII 1000BASE-X |          |   |          | 1000BASE-X |

| 10G     | ✓                                       | <b>√</b>                                           |          |   |          |            |

| 5G      | ✓                                       | ✓                                                  | ✓        |   |          |            |

| 2.5G    | ✓                                       | ~                                                  | <b>V</b> | ✓ |          |            |

| 1G      | ✓                                       | <b>V</b>                                           | ✓        | ✓ | -        | ✓          |

| 100Mbps | <b>√</b>                                | ~                                                  | ✓        | ✓ | <b>√</b> |            |

Table 1.2 System Interface SerDes Operating Modes

**Note:** In Table 1.2, the green check marks indicate native rate support and the orange check marks indicate port-based frame rate-adaptation via one of the native SerDes modes.

## 1.4 Power-On

The device family is designed to perform the following operations at boot:

- Power-up calibration of internal VCOs and variable power supplies (if variable supply operation is enabled)

- Provision stored default values<sup>†</sup>

- Calibration of the analog front-end

<sup>&</sup>lt;sup>†</sup> AQR113-AQR114-AQR115/AQR113C-AQR114C-AQR115C can store in its firmware image a list of registers with default values that can be overwritten with user-specified values on power-up. To perform this, use the web-based Aquantia Firmware Provisioning Tool, which allows the PHY to be personalized for certain modes of operation.

- Autonegotiation<sup>†</sup>

- Perform training (as required)

- · Verify error-free operation

- Enter steady state

## 1.5 Cable and Board Diagnostics

The device family implements a powerful cable diagnostic algorithm that accurately measures all of the TDR and  $TDT^{\ddagger}$  sequences within the group of four channels. This algorithm transmits a pseudo-noise sequence with an amplitude of less than 300mV for a brief period of time, and from this, it converges the 10GBASE-T equalizers on all of the other channels. From the results of this measurement, the length of each pair, the top impairment along the pair, and the impedance of the cable are flagged.

These measurements are reported using cable propagation characteristics of 4.83ns/m and these are presented in the Global MMD register map (for details, see "References" on page 107). For board diagnostics, the device family detects opens and shorts on MDI pins or faulty transformers, and these results are stored in the MDIO register.

**Note:** The device family is an AQrate PHY and compliant with both the IEEE 802.3an/bz standard and the NBASE-T Alliance PHY specifications. In addition, this device family also supports cable diagnostics that meet the latest set of industry-standard switch and port specifications.

## 1.6 Debug and Diagnostics Tools

The device family supports a full suite of network and system loopbacks at all supported rates, and these loopbacks are shown in Figure 1.1 on page 22.

In addition to the loopbacks, the device family supports CRC-32 packet checking on both the receive and transmit traffic at all supported rates, and it also maintains 1-second interval packet counters for both errored and good packets.

Finally, the device family is able to generate all of the IEEE test mode patterns, as well as CRPAT generation, and checking in both the line and system directions. It also supports (via the API) the ability to generate an eye diagram for each of the receive lanes.

<sup>&</sup>lt;sup>†</sup> AQrate supports an automatic downshift capability (as specified in Table 6.9.62 on page 409) for configuring autonegotiation settings.

<sup>&</sup>lt;sup>‡</sup> The cross-channel impulse responses.

Figure 1.1 Loopbacks

On the KR interface, the device family supports  $x^9$ ,  $x^{31}$ , square wave, pseudo-noise generation and checking, as well as CRPAT generation and checking. Figure 1.1 illustrates the supported loopbacks in the device family:

- System interface/system loopback PCS loopback

- Network interface/system loopback PMA loopback

- System interface/network loopback PHY-XS loopback

- Network interface/network loopback

- A-B/C-D cable loopback

## 1.7 API and Programming Tools

Associated with the device family are the following software tools:

- A set of ANSI C register structures for each MMD that provide bit level and word level access to all of the device family registers.

For documentation about these structures, refer to the API document ("API", Aquantia Corporation" on page 107).

- An ANSI C API that provides a set of structures and associated Set/Get functions to implement all normal PHY operations. This API is written with register name abstraction so that the registers are visible, and it is documented using Doxygen, which allows users to view the code and click on a variable to get the datasheet definition.

This API also contains functions on how to burn new FLASH images, as well as perform other MDIO boot-load operations. For documentation about these and other operations, refer to the API document ("API", Aquantia Corporation" on page 107).

## 1.8 MACsec

The device family supports integrated MACsec at all network rates, and it also supports the following modes of operation:

- Autonomous Operation: In this mode, the device family does all of the gap insertion and other tasks required to add the MACsec headers and integrity check values (ICVs). This is done via two integrated MACs and 64KB of buffering in each direction. These MACs monitor the buffer fill-depths, and also generate port-based PAUSE frames in either direction, as required. In addition, it responds to port-based PAUSE frames (802.1Qbb class-based PAUSE frames) that are passed through.

- **Cut-through Operation**: In this mode, the device family expects to receive packets from the system pre-gapped, and all the device family does is insert the MACsec headers and ICVs.

- **Bypass Operation**: In this mode, the MACsec block is completely bypassed, in scenarios where MACsec in the PHY is not necessary.

### 1.8.1 General Features

The MACsec supports the following general features:

AES-256, AES-128, and clear operation with simultaneous mixed usage, where the encryption and decryption are decided on a per-packet basis based on an access control list (ACL) that looks either at the MACsec header or fields in the packet header (explicit or implicit secure channel identification).

- 16 secure channels (SCs), with two security associations (SAs) per SC with automatic roll-over between SAs on a programmable packet number (PN) value.

- 3) Full support of the 802.1AE MIB (for details, see "Media Access Control (MAC) Security", IEEE STD-802.AE-2006, IEEE Standards Office, The Institute of Electrical and Electronics Engineers, Inc., 3 Park Avenue, New York, NY 10016-5997, USA, April 17, 2003).

- 4) Per packet Galois counter mode (GCM) authentication on the ICV (16 or 32 byte).

- Strict and out-of-order replay checking with a per SC programmable 32-bit (for example, from 0 to 2<sup>31</sup>-1 packets) replay window for the out-of-order mode.

- 6) A programmable confidentiality offset per SA of between 0 and 127 bytes offset.

| Per SA | Name                                         | Description                                                                                  |

|--------|----------------------------------------------|----------------------------------------------------------------------------------------------|

|        | Ingress Control Packets                      | The number of ingress control packets received                                               |

| x      | Ingress Untagged Hit Packets                 | The number of ingress untagged packets received that passed the implicit SCI lookup          |

|        | Ingress Untagged Miss Packets                | The number of ingress untagged packets received that had no implicit SCI lookup              |

| x      | Ingress Hit Packets Dropped                  | The number of ingress packets that passed the SCI lookup, but were tagged for Drop           |

|        | Ingress Tagged Packets                       | The number of ingress packets with a MACsec header                                           |

|        | Ingress Tagged Packets Bad Tag               | The number of ingress packets with an invalid SecTag or packet number (PN).                  |

|        | Ingress Tagged Packets SCI Miss              | The number of ingress tagged packets with a missing SCI or an SCI that was not in the table. |

| X      | Ingress Tagged Packets<br>Non-Operational SA | The number of ingress packets with an identified, but non-operational SA.                    |

| X      | Ingress Packets Authentication<br>Fail       | The number of ingress packets that fail authentication                                       |

7) A MIB containing the following additional statistics counters:

#### Table 1.3 Additional Ingress MACsec Statistics

| Per SA | Name                        | Description                                                                    |  |

|--------|-----------------------------|--------------------------------------------------------------------------------|--|

| x      | Ingress Packets Replay Fail | The number of ingress packets that fail the replay check                       |  |

| x      | Ingress Packets Late        | The number of ingress packets that fail the replay check because they are late |  |

| X      | Ingress Packets OK          | The number of ingress packets that pass all checks                             |  |

|        | Ingress Reserved Counter 0  |                                                                                |  |

|        | Ingress Reserved Counter 1  |                                                                                |  |

|        | Ingress Reserved Counter 2  |                                                                                |  |

|        | Ingress Reserved Counter 3  |                                                                                |  |

Table 1.3 Additional Ingress MACsec Statistics (continued)

| Per SA | Name                      | Description                                                                           |

|--------|---------------------------|---------------------------------------------------------------------------------------|

|        | Egress Control Packets    | The number of egress control packets transmitted                                      |

|        | Egress Packets Unknown SA | The number of egress packets transmitted with an unknown SA (Table Miss and Untagged) |

|        | Egress Untagged Packets   | The number of egress packets transmitted without a MACsec header                      |

| X      | Egress Protected Packets  | The number of egress packets transmitted with a valid ICV (authenticated + encrypted) |

#### Table 1.4 Additional Egress MACsec Statistics

### 1.8.2 Ingress Lookup

On ingress, the MACsec block can perform the following tasks:

- 1) Remove the MACsec header.

- 2) Strip zero-padded bytes for runt packets.

- 3) Corrupt the FCS for any failed packets.

- 4) Run a consistency check against another ACL.

- 5) Count control packets.

- 6) Enforce maximum MTU sizes via either truncation or FCS corruption.

- 7) Generate an interrupt on security failure.

- 8) Look up the implicit SCI based on the following fields:

- a) MAC DA 48 bits

- b) MAC SA 48 bits

- c) Payload Ether-Type 16 bits

- d) QTAG\_VLD and STAG\_VLD (Ingress Consistency Check only)

- e) TCI/AN 8 bits (Note that TCI needs preprocessing as per Clause 9.1.2)

- f) SCI 64 bits

- g) VLAN 12 bits (Ingress Consistency Check only)

- *h*) Any four programmable bytes within the first 64 bytes of the packet

- *i*) Origin (loopback versus front panel) ingress table only

- *j*) Valid bit

- 9) Lookup the implicit SCI based on the following fields:

- a) The MACsec block for the device family supports the ability to calculate the following categories: EtherType, VLAN, and the User-Priority of a packet by using a 32-bit mapping table provided with each entry in the SCI lookup. There is one mapping table per port and the mapping table contains the following fields:

| Bit | Name       | Function                               |  |

|-----|------------|----------------------------------------|--|

| 31  | PARSE_QTAG | Enables parsing 802.1Q VLAN tags       |  |

| 30  | PARSE_STAG | Enables parsing 802.1Q MST tags        |  |

| 29  | PARSE_QINQ | Enables Q-in-Q parsing                 |  |

| 28  | QTAG_UP_EN | Enables the use of the 802.1Q priority |  |

Table 1.5 "Per SCI" 32-Bit Mapping

| Bit   | Name       | Function                                             |

|-------|------------|------------------------------------------------------|

| 27    | STAG_UP_EN | Enables the use of the 802.1S priority               |

| 26:24 | DEF_UP     | Represents default user-priority                     |

| 23:0  | MAP_TBL    | Represents priority mapping for 802.1Q priority tags |

| Table 1.5 "Per SCI" 32-Bit Mapping | (continued) | 1 |

|------------------------------------|-------------|---|

|------------------------------------|-------------|---|

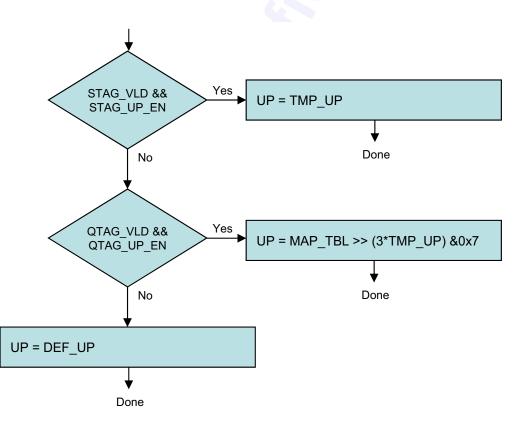

**Note:** The EtherType, VLAN, and User-Priority packet categories are determined using the mapping table fields (listed in Table 1.5):

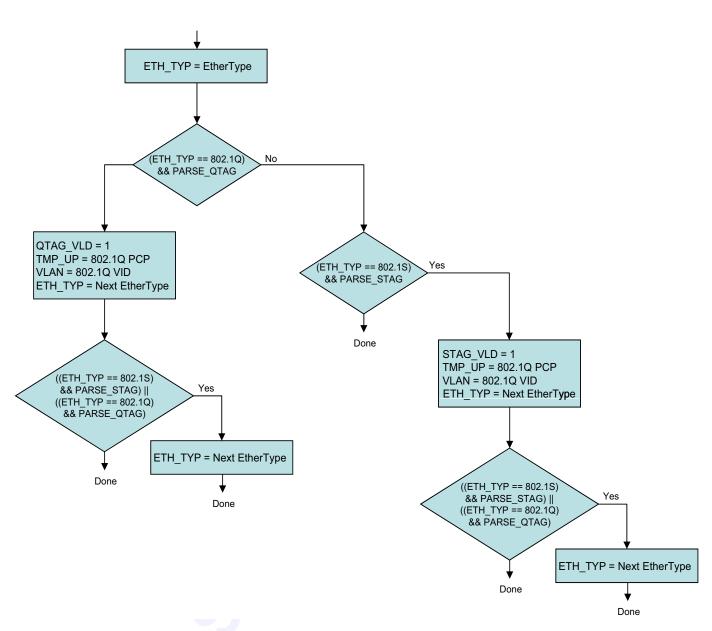

*b)* EtherType and VLAN resolution is determined, as shown in Figure 1.3 on page 28.

**Note:** 802.1S and 802.1Q EtherTypes are provisionable per port.

*c*) User priority is resolved, as shown in Figure 1.2.

Figure 1.2 User Priority Resolution

Figure 1.3 EtherType and VLAN Parsing Algorithm

*10*)Support a provisioned definition of the 802.1Q and 802.1S EtherType tags.

11)Support the following actions from the SCI lookup:

- a) Decrypt/Authenticate (provisioned per SA)

- b) Drop

- c) Bypass

- d) Re-direct (capture to debug)

- 12)Support globally changing the action for the lookup on a table basis (for allowing rapid debug).

### 1.8.3 MACsec Ingress Post-Processing

After decryption and during post-processing, the MACsec block can perform the following tasks:

- 1) Remove or leave the MACsec header.

- 2) Over-write the PN field of the MACsec header with provisionable data when operating in MACsec header non-removal mode.

- 3) Strip zero-padding bytes from the packet according to the MACsec header short-length (SL) field.

- 4) Grow short packets that are not SL stripped back to 64-bytes (for example, the MACsec packet is ≥ 64 bytes, but after removal of the MACsec, the packet is sub-64 bytes).

- 5) Support the corruption of the FCS on packets which fail any enabled security check in both the ingress and egress directions.

- 6) Support a 32-entry per-port consistency check after decryption based on:

- a) SAI\_HIT

- b) SAI[3:0]

- c) VLAN[11:0]

- d) VLAN\_VLD

- *e*) ETYPE\_VLD (EtherType > Programmable maximum length)

- f) Payload EtherType[15:0]

- *g)* Each of these fields shall be maskable and have a single action bit indicating whether to drop the packet or not.

- *h*) The port shall also support a 33rd entry that indicates what to do with a miss.

- 7) Generate an interrupt on security failure.

#### **1.8.4 Egress Processing**

On egress, the MACsec block can perform the following tasks:

- 1) Support the same lookup and mapping mechanism as is used in the ingress direction.

- *2)* Support the ability to perform lookup with and without the presence of a MACsec header.

- 3) Zero pad short packets and mark the SL field in the MACsec header accordingly.

- 4) Fill in the remainder of the MACsec header, given provided TCI and SL fields. This means that the MACsec EtherType (88\_E5), AN, PN, and optional SCI are filled in by the PHY.

- 5) Support the following actions from the SCI lookup:

- a) Encrypt/Authenticate (provisioned per SA)

- b) Drop

- c) Bypass

- d) Re-direct (loopback or capture to debug)

- 6) Count control packets.

- 7) Enforce maximum MTU sizes via either truncation or FCS corruption.

- 8) Support globally changing the action for the lookup on a table basis (for allowing rapid debug).

- 9) Generate an interrupt on security failure.

### 1.8.5 MACs

The MACs in the MACsec block can perform the following tasks:

- 1) Support ingress and egress MIBs with per-EtherType 40-bit counters and RMONs (packet drop and packet pass-through).

- Support an in store-and-forward mode that is a port-based PAUSE flow-control in both directions, with programmable thresholds and hysteresis.

- *3)* Ignore 802.1Qbb class-based PAUSE frames and pass them through the PHY.

- Support programmable ingress and egress inter-packet gap (IPG) of between 4 and 63 bytes<sup>†</sup>.

- 5) Support processor access to the MAC buffers for debug.

- 6) Support the ability to recognize control packets via the following criteria:

*a*) MAC\_DA[47:4] = 01\_80\_C2\_00\_00\_0

- *b*) MAC\_DA[47:4] = 01\_00\_0C\_CC\_CC\_CC

- c) 8 per port programmable MAC\_DA addresses

- d) 8 per port programmable EtherType matches

- e) 1 per port programmable MAC\_DA with Do Not Care mask

- *f*) 2 sets of per port programmable MAC\_DA and EtherType combinations

**Note:** These are provisionable on a port-by-port basis.

7) Support sending and receiving up to 512 byte packets in both the ingress and egress directions.

Both the ingress and egress ports shall each support a programmable MAC address, and the ability to disable operation of these ports.

<sup>&</sup>lt;sup>†</sup> With each packet having a fixed 7-byte preamble and 1-byte start-of frame delimiter (SFD).

8) Support a non-destructive L2 system loopback, with a programmable MAC address and an enable. This loopback FIFO *must* be 512 bytes in size and support head and tail drop (provisionable). This FIFO *must* be capable of being stopped at any time (on a packet-by-packet granularity) and the packet(s) within read out.

The depth of this FIFO needs to be programmable. Packets larger than the programmable size can be dropped or truncated (programmable). Packets that are dropped due to overflow *must* be counted on a per SA basis using an 8-bit counter (as saturating, and clear-on-read).

These looped-back packets *must* be accounted for in a similar set of counters to the ingress MAC, as they are not accounted for there (for example, the loopback after ingress MAC).

- *9)* Enforcing a per priority, programmable maximum MTU size with an option for either truncation or FCS corruption.

- *10*)Support the following statistics on ingress and egress (as shown in Table 1.6):

| Egress | Ingress | Per<br>Priority | Name                           | Description                                             |

|--------|---------|-----------------|--------------------------------|---------------------------------------------------------|

| x      | X       |                 | Total Packets                  | The total number of packets (good + bad)                |

| x      | x       | x               | Total Packets (per priority)   | The total number of packets (good + bad) (per priority) |

| х      | X       |                 | Dropped Packets                | Packets dropped for any reason                          |

| X      | x       | x               | Dropped Packets (per priority) | Packets dropped for any reason (per priority)           |

| X      | X       |                 | Bytes                          | Total frame octets                                      |

| x      | x       | X               | Bytes (per priority)           | Total frame octets (per priority)                       |

| X      | x       | 5               | Broadcast Packets              | Total broadcast packets with a good FCS                 |

| X      | x       |                 | Multicast Packets              | Total multicast packets with a good FCS                 |

| Х      | x       |                 | Fragments                      | Frames < 64 bytes with a bad FCS                        |

| X      | x       |                 | Jabbers                        | Frames > MTU <sub>MAX</sub> with a bad FCS              |

Table 1.6 MAC Statistics

| Egress | Ingress | Per<br>Priority | Name                         | Description                                                                      |

|--------|---------|-----------------|------------------------------|----------------------------------------------------------------------------------|

|        | x       |                 | CRC Align Errors             | Frames with a bad FCS that are neither fragments nor jabbers in-the-clear        |

| x      |         |                 | Bad Packets                  | Frames with a bad FCS                                                            |

| x      |         |                 | Good Packets                 | Frames with a good FCS                                                           |

|        | x       |                 | Undersize Packets            | Frames with a good FCS less than 64 bytes                                        |

| X      | x       |                 | 64 Byte Packets              | The total number of packets (good + bad) of 64 byte length                       |

| x      | x       |                 | 65 To 127 Byte Packets       | The total number of packets (good +<br>bad) between 65 and 127 byte<br>length    |